Высокопроизводительное семейство 32‑битных контроллеров Microchip

Ядро M14K и microAptiv

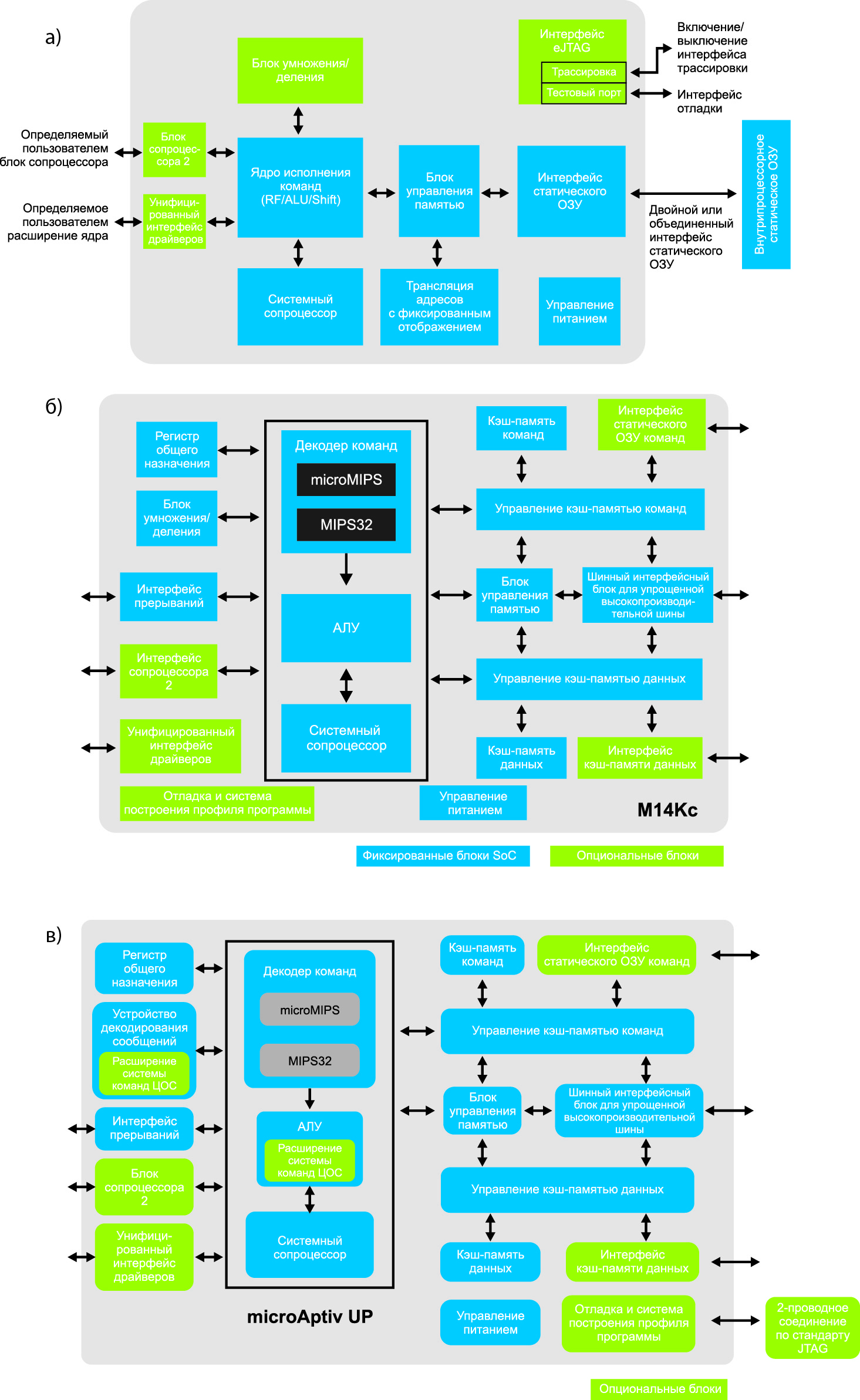

Ядро M14K (и версия с кэш-памятью M14Kc, рис. 1б) является развитием ядра M4K (рис. 1а), в котором реализована система команд microMIPS, которая содержит как 16-, так и 32‑битные инструкции, что позволяет увеличить плотность кода и пропускную способность ядра. Система команд microMIPS уменьшает размер кода как минимум на 30% при сохранении быстродействия на уровне ядра M4K [2].

Рис. 1. Структурная схема ядра:

а) M4K;

б) M14Kс

в) структурная схема ядра microAptiv, микропроцессорный вариант (MPU)

Ядро microAptiv (рис. 1в) — это следующая ступень развития ядра MIPS32. Основанное на M14Kс, ядро microAptive получило большее быстродействие, дополнено ЦОС-расширением ядра MIPS и новыми возможностями защиты памяти и интерфейса отладки.

Основное улучшение архитектуры microAptiv — это ЦОС-расширение ядра и системы команд (MIPS32 DSP Application Specific Extension, ASE), позволяющее выполнять за один такт любую команду из полного набора ЦОС и команд умножения с накоплением (Multiply and Accumulate, MAC).

Расширение MIPS32 DSP ASE — это комбинация аппаратной и программной частей, которая служит для улучшения возможностей применения ядра в задачах ЦОС. При разработке DSP ASE специалисты старались как можно больше задействовать существующие цепи ядра для того, чтобы по возможности не влиять на площадь кристалла и тактовую частоту.

Ядро microAptive, как M14K и M4K, имеет два независимых 5‑стадийных конвейера: конвейер ядра, который выполняет стандартные команды (загрузка/хранение, вычисления, переходы), и конвейер MDU (Multiply Divide Unit). Оба конвейера работают параллельно и независимо друг от друга. Расширение MIPS32 DSP ASE использует оба конвейера ядра и MDU для выполнения своих инструкций.

В дополнение к операциям целочисленного деления и умножения конвейер MDU выполняет ЦОС-инструкции с командами умножения и доступом к аккумуляторам (microAptive имеет до четырех 64‑битных аккумуляторов). Кроме того, реализованы переадресации внутри конвейера ядра, а также между АЛУ и MDU, когда результат предыдущей команды посылается непосредственно к текущей, в обход обновления регистров.

Расширенный набор инструкций добавляет 159 ЦОС-команд, включая 70 команд, поддерживающих множественный поток данных (Single Instruction Multiple Data, SIMD), и 38 команд умножения/MAC. Специализированный ЦОС-набор включает ряд арифметических инструкций с опциями насыщения и округления, операции сравнения/выборки, загрузки и накапливания и команды упаковки/распаковки данных, которые обычно используются в функциях масштабирования.

В дополнение к обычно встречающимся операциям DSP ASE также включает некоторые функции, повышающие производительность. Примером являются функции извлечения произвольных битов, например, из входного потока. Другие функции позволяют эффективно обрабатывать комплексные числа. Набор команд также включает в себя новый и эффективный способ для поддержки виртуальных кольцевых буферов.

Инструкции умножения/MAC работают со встроенным массивом умножителей 32×32, который выполняет 32×32, 16×16, две по 16×16, две 16×8 и две 8×8 операции умножения за один такт. Результаты умножения/MAC инструкций могут быть записаны на любом РОН или аккумуляторе.

Дополнительный аппаратный модуль ЦОС позволяет существенно повысить быстродействие для приложений, для которых необходимы математические вычисления. Так, в сравнении с ядром M14K большинство ЦОС-инструкций требуют в два раза меньше времени, а для реализации 16‑битного КИХ-фильтра (к = 32) нужно на 75% меньше циклов [4] (рис. 2).

Высокое быстродействие и функционирование ядра микроконтроллера в реальном времени обеспечиваются быстрой реакцией на прерывание, одноцикловым доступом к статическому ОЗУ и Flash-памяти. Возможности отладки также были улучшены с добавлением возможности использования 2‑проводного JTAG-интерфейса. В дополнение microAptive предоставляет повышенный уровень секретности при помощи модуля защиты памяти и новых защищенных возможностей отладки.

Ядро microAptiv включает контроллер кэш-памяти и модуль управления памятью (Memory Management Unit, MMU), что делает его пригодным для использования операционных систем реального времени, требующих управления виртуальной памятью. Ядро microAptive конфигурируется для поддержки трех систем команд: MIPS32, MIPS32 + microMIPS или только microMIPS. В режиме системы команд microMIPS ядро microAptiv достигает быстродействия 3,09 CoreMark/МГц и 1,57 DMIPS/МГц.

Ядро microAptive доступно в двух вариантах:

- microAptiv MCU ядро — микроконтроллерный вариант без кэша с быстродействующим интерфейсом со статической памятью ОЗУ;

- microAptiv MPU ядро — микропроцессорный вариант с контроллером кэш-памяти, контроллером управления памятью с буфером динамической трансляции адресов (TLB MMU), что позволяет запускать операционные системы, которые оперируют виртуальной памятью, например Linux или Android.

Сравнение архитектур MIPS microAptive и ARM Cortex-M4

Наиболее близким конкурентом ядра microAptive является Cortex-M4. Обе архитектуры microAptive и Cortex-M4 были разработаны для микроконтроллеров с возможностью выполнения задач ЦОС. Однако microAptive предлагает более богатый набор микроконтроллерных и ЦОС-возможностей. Сравнение основных отличий приведено в таблице 1.

|

Особенность |

MIPSmicroAptiv |

ARM Cortex-M4 |

|

Длина конвейера |

5 |

3 |

|

Версия с кэшем/MMU |

Да |

Нет |

|

Система команд |

MIPS32 и microMIPS |

Thumb2 |

|

Число инструкций |

300 |

155 |

|

РОН (наборов) |

32 (16) |

16 (1) |

|

Поддержка Closely coupled memory |

Да |

Нет |

|

Реакция на прерывания |

10 циклов |

12 циклов |

|

Трассировка команд |

Да |

Нет |

|

Быстрый канал отладки |

Да |

Нет |

|

ЦОС-возможности |

||

|

Число ЦОС-инструкций |

159 |

80 |

|

Число SIMD-команд |

70 |

38 |

|

Число команд умножения/MAC |

38 |

29 |

|

Выделенный DSP/MDU |

Да |

Нет |

|

Аккумулятор |

Да (64 бит ×4) |

Нет |

|

16×8, два 8×8 умножителя/MAC |

Да |

Нет |

|

Команды сдвига |

Да |

Нет |

|

Команды сравнения/Pick |

Да |

Нет |

Ядро Cortex-M4 основано на Cortex-M3, к которому добавлены простые функции ЦОС. По тестам производительности ядро microAptiv показывает большую на 25% (DMIPS) и 40% (CoreMark) производительность относительно Cortex-M4 (рис. 3).

При оценке возможностей цифровой обработки сигналов отличия становятся еще более существенными. Расширение DSP ASE ядра microAptiv имеет свой отдельный конвейер, работающий параллельно конвейеру ядра, тогда как в Cortex-M4 существует только один конвейер. Ядро microAptiv имеет до четырех 64‑битных аккумуляторов и дополнительные наборы РОН для хранения результатов ЦОС-инструкций, тогда как Cortex-M4 не имеет аккумуляторов и использует общий с АЛУ набор РОН, который к тому же состоит только из 16 регистров (против до 16 наборов из 32 регистров у microAptiv). Ядро microAptiv имеет в два раза больше ЦОС-команд, больший набор функций и больше SIMD- и MAC-инструкций. И наконец, microAptiv имеет более гибкие операнды сдвига/масштабирования.

Компания ARM предоставляет програм-мную библиотеку для Cortex-M4, называемую Cortex Microcontroller Software Interface Standard (CMSIS). Включенный в CMSIS набор ЦОС-алгоритмов аналогичен представленным алгоритмам в библиотеке MIPS DSP Library. Отличия в производительности одних и тех же алгоритмов приведены на рис. 3. Результаты были получены для платы ST32FM4 Discovery с использованием отладочной платформы Keil MDK. Результаты для ядра microAptiv были измерены на плате MIPS SEAD‑3 с применением компилятора Mentor Sourcery CodeBench gcc. Полученные результаты доказывают существенное превосходство ядра microAptive при выполнении наиболее часто применяемых ЦОС-алгоритмов.

Библиотека MIPS DSP Library содержит функции БПФ (FFT‑16, FFT‑32), фильтрации (IIR16, FIR, LMS), векторной математики и функции кодирования и декодирования видео H264. Эти алгоритмы были разработаны и оптимизированы с учетом описанных свойств ядра. Критические части кода написаны на ассемблере, другие, менее используемые и некритические подпрограммы реализованы на Си. Версия ЦОС-библиотеки, оптимизированная под ядро microAptiv, использует DSP ASE по возможности в формате microMIPS.

PIC32MZ с ядром microAptive

Компания Microchip запускает в производство высокопроизводительные 32‑разрядные контроллеры PIC32MZ на основе ядра microAptiv. Новые контроллеры PIC32MZ семейства EC (Embedded Connectivity) имеют уникальные параметры, прежде не встречавшиеся в продукции Microchip. Основанные на микропроцессорном варианте ядра microAptiv MPU, с ЦОС-расширением команд, контроллером кэш-памяти и контроллером управления памятью с буфером динамической трансляции адресов TLB MMU, микропроцессоры имеют до 2 Мбайт Flash-памяти программ, 512 кбайт ОЗУ (табл. 2) и тактовую частоту до 200 МГц [4].

|

Параметры |

PIC32MX |

PIC32MZ |

|

Ядро |

M4K |

microAptive MPU |

|

Тактовая частота, МГц/ быстродействие, DMIPS |

80/125 |

200/330 |

|

Размер памяти Flash/ОЗУ, кбайт |

512 (+12K Boot Flash)/ 128 |

2048 (+160K Boot Flash)/ 512 |

|

Кэш-память |

256 байт предвыборки команд |

16 кбайт инструкций и 4 кбайт данных |

|

РОН (число наборов) |

32 (2) |

32 (8) |

|

ЦОС-команды |

Нет. Отдельный MDU c поддержкой MAC-команд |

Да. Отдельный MDU с поддержкой MAC-команд, ЦОС- и SIMD-команды, четыре 64-битных аккумулятора |

|

Интерфейсы внешней памяти |

– |

EBI (до 64 Мбайт) и SQI (до 64 Мбайт) |

|

DMA |

8 (+ до 8 для высокоскоростной |

8 (+ до 14 для высокоскоростной периферии: USB, Ethernet, SQI, EBI, криптомодуля) |

|

USB-интерфейс |

USB FS Host, Device и OTG |

USB HS/FS Host, Device и OTG |

|

Криптомодуль |

Нет |

Да, поддержка AES, 3DES, SHA, MD5 и HMAC, RND-генератор |

Особенности PIC32MZ

Память программ (Flash)

Flash-память контроллеров имеет две панели размером до 1 Мбайт и две области загрузчика (Boot-сектор) по 80 кбайт каждый, то есть суммарный размер памяти 2 Мбайт + 160 кбайт. Подобная организация памяти позволяет иметь независимые секции и использовать часть памяти для эмуляции EEPROM или обновлять прошивку контроллера «на лету» без потери управления на время записи Flash-памяти. У контроллеров PIC32MZ есть возможность обнаружения и коррекции ошибок (Error Correction Code, ECC), что увеличивает надежность системы. Специальный регистр конфигурации позволяет указать, какая область памяти будет основной, то есть из какой области выполняется программа при старте.

Модуль предвыборки команд в PIC32MZ может обнаружить два типа ошибок Flash-памяти: ошибку двух бит (ECC Double-bit Error Detected, DED) и одиночную ошибку (ECC Single-bit Error Corrected, SEC). Двойная ошибка DED является критичной, и ее обнаружение приведет к немаскируемому прерыванию. Одиночная ошибка памяти SEC не критична (исправима), и такая ошибка может быть выявлена через установку прерывания. При обнаружении ошибки пользовательский код может перезаписать проблемный участок памяти.

Высокоскоростная периферия

Высокоскоростная периферия включает интерфейсы USB HS, Ethernet, шины EBI (Extended Bus Interface) и SQI (Serial Quad Interface). Интерфейс EBI позволяет подключать по параллельному интерфейсу внешнюю память, дисплеи, видеокамеры и пр. Адресуемая через EBI внешняя память (до 64 Мбайт) отображается по умолчанию в область KSEG2 контроллера.

Интерфейс SQI предназначен для подключения последовательной памяти (до 64 Мбайт), которая также отображается в сегменте KSEG2. Интерфейс SQI обеспечивает быстрое обращение к памяти через два выделенных канала DMA, а также позволяет выполнять код во внешней памяти.

Криптомодуль

Модуль поддержки криптофункций призван ускорить приложения, использующие криптографические алгоритмы. Он обеспечивает поддержку AES, DES/TDES, SHA, MD5, HMAC и др., а также генератор случайных и псевдослучайных чисел с настраиваемым полиномом (до 64 бит).

Низкоскоростная периферия

К низкоскоростной периферии относятся интерфейсы CAN, UART, I2S/SPI и I2C.

Контроллеры PIC32MZ имеют семь раздельных периферийных шин. Частоту каждой шины настраивают индивидуально, что позволяет наборы периферийных модулей тактировать разной частотой.

Порты ввода/вывода в контроллерах PIC32MZ могут переопределять функции (Peripheral Pin Select, PPS) и имеют возможность подключения встроенной подтяжки к напряжению питания или «земле». Часть портов толерантна к напряжению 5 В.

Модуль АЦП

Модуль АЦП существенно отличается от АЦП предыдущих контроллеров Microchip. Дифференциальный АЦП обеспечивает разрешение 12 бит, имеет конвейерную архитектуру и шесть УВХ, что позволило увеличить быстродействие до 28 млн преобразований в секунду. Наличие шести УВХ позволяет производить одновременную выборку шести каналов. Пять каналов АЦП подключаются к фиксированным выводам контроллера, а шестой имеет возможность измерения множества каналов. Все каналы АЦП могут быть включены в автоматизированный список сканирования (scan list). Часть каналов имеют выделенные триггеры на запуск измерения, а другая часть — общий триггер запуска. В модуль АЦП входят шесть цифровых фильтров передискретизации для увеличения разрядности до 16 бит и шесть цифровых компараторов — для формирования прерываний при попадании сигнала в заданное окно результатов.

Средства разработки

Компания Microchip предлагает бесплатную среду разработки MPLAB X, поддерживающую все 8-, 16‑ и 32‑битные контроллеры, а также C/C++ компиляторы для PIC32. Текущая версия компилятора основана на GNU Compiler Collection (GCC) v4.5.2.

Вместе с анонсом PIC32MZ компания Microchip объявила о выходе новой системы разработки программного кода для 32‑разрядных микроконтроллеров — MPLAB Harmony. Новый фреймворк включает в себя программные драйверы, библиотеки и ОСРВ, разработанные не только Microchip, но и сторонними компаниями. MPLAB Harmony предоставляет возможность использовать бесплатные и лицензируемые программные решения. Сейчас Harmony содержит USB, TCP/IP-стеки, графические библиотеки, а также программные продукты сторонних производителей: Express Logic, FreeRTOS, InterNiche, WITTENSTEIN High Integrity Systems и wolfSSL. В создании MPLAB Harmony участвовали несколько компаний; благодаря их совместным усилиям сократилось число возможных ошибок при интеграции нескольких решений в одно, что в свою очередь сильно упрощает процесс написания программного кода для микроконтроллеров и позволяет быстрее выпустить товар на рынок.

Архитектура MIPS известна много лет и поддерживается многими производителями средств разработки.

Для поддержки сторонних разработчиков MIPS Technologies создала MIPS Alliance Program (MAP) [5]. В альянс входит более ста компаний, которые предлагают сотни решений для поддержки MIPS-архитектуры: компиляторы, отладчики, интегрированные среды и комплексы разработки (IDE, EDA), операционные системы и прикладные библиотеки.

Перечислим некоторых партнеров альянса, которые предоставляют поддержку MIPS-платформы:

- Операционные системы реального времени (RTOS) предоставляют такие компании, как Express Logic, Mentor Graphics, Micrium, Segger, Green Hills Software, Wind River, CMX, FreeRTOS, Interniche Technologies, AVIX-RT, Pumpkin и RoweBots.

- Отладчики, эмуляторы и программаторы предлагают Ashling, Lauterbach, Macraigor, Coreli и Elnec.

- Программные средства разработки, включая компиляторы, IDE и EDA/ESL, предлагают компании Green Hills, Mentor Graphics, Synopsys, Cadence, Magma, mikroElektronika и RoweBots.

- Модели для симуляции выпускают Carbon и Imperas.

Некоторые Open Source и бесплатные проекты:

- OpenOCD (бесплатный и открытый проект, предоставляющий внутрисхемную отладку, программирование и граничное сканирование).

- EJTAGproxy утилита для подключения GNU отладчика к PIC32 микроконтроллерам через JTAG или ICSP адаптер. Реализует стандартный последовательный протокол GDB для удаленной связи. Можно использовать совместно с Eclipse, DDD, Insight или другими совместимыми отладчиками. Поддерживает: PICkit 2, PICkit 3, Olimex ARM-USB-ххх, Olimex MIPS-USB-ххх, Bus Blaster v2 (JTAG-адаптер от Dangerous Prototypes) и Flyswatter (JTAG-адаптер от TinCanTools).

- Программатор Pic32prog для программирования Flash-памяти контроллеров PIC32. Поддерживаемые программаторы и протоколы: PICkit 2, PICkit 3, Olimex ARM-USB-ххх, Olimex MIPS-USB-ххх, Bus Blaster v2 (JTAG-адаптер от Dangerous Prototypes) и Flyswatter (JTAG-адаптер от TinCanTools), AN1388 HID bootloader (Microchip).

- chipKIT — Arduino-совместимая OpenSource платформа с бесплатной средой разработки и C++ компилятором.

- TNKernel — операционная система реального времени.

- Кроссплатформенный фреймворк QP (Quantum Platform) от Quantum Leaps — средство разработки приложений для встраиваемых систем в виде конечных автоматов на основе UML диаграмм состояний.

Выводы

MIPS предоставляет ядра, составляющие серьезную конкуренцию ARM-платформам. Новые процессоры PIC32MZ Embedded Connectivity, основанные на процессорном варианте ядра MIPS microAptive, имеют уникальные параметры и могут применяться как в задачах управления, так и в задачах цифровой обработки сигналов. Существенное превосходство в быстродействии по сравнению с процессорами ARM Cortex дает возможность выполнять одни и те же задачи быстрее или на более низкой частоте, что позволит существенно уменьшить потребление системы.

- Афанасьев И. Микропроцессорные 32‑битные ядра MIPS для высокопроизводительных встраиваемых систем // Компоненты и технологии. 2014. № 3.

- MicroMIPS CramsCode. New Processor Cores Introduce Denser 16/32‑Bit Instruction Set. 11/16/09-01. mpronline.com

- An Introduction to MIPS32 microAptiv Processor Cores — The Convergence of MCU/MPU and DSP. MIPS Technologies, Inc. mips.com

- PIC32 Family Reference Manual. microchip.com

- Beyond the Hype: MIPS — the Processor for MCUs. MIPS Technologies, Inc.

- mips.com

- arm.com

отправка...

отправка...